驱动电路及传输系统的制作方法-j9九游会真人

1.本发明涉及集成电路技术领域,特别是涉及一种驱动电路及传输系统。

背景技术:

2.动态随机存取存储器(英文:dynamic random access memory,简称:dram)是一种半导体存储器,主要的作用原理是利用电容内存储电荷的多寡来代表一个二进制比特(英文:bit)是1还是0。

3.随着dram速度的提高,需要进一步减小发送器的输出阻抗,如由40ω减小至34ω。相关技术中,通过增加驱动晶体管的并联数量,可以减小发送器的输出阻抗。

4.然而,直接增加驱动晶体管的并联数量,需要相应增加预驱动电路和对应的信号线,使得引脚连接区域的面积增大较多,影响芯片性能。

技术实现要素:

5.基于此,有必要提供一种可以不会影响到芯片性能的驱动电路及传输系统。

6.第一方面,提供了一种驱动电路,所述驱动电路包括:

7.第一上拉驱动模块,包含多个第一上拉驱动器,用于根据上拉指示信号和驱动选择信号开启至少一个所述第一上拉驱动器,所述驱动选择信号用于选择所述第一上拉驱动器的开启数量,所述第一上拉驱动器用于生成具有预设电压的输出信号;

8.上拉控制模块,用于根据所述上拉指示信号生成上拉控制信号;

9.第二上拉驱动模块,与所述上拉控制模块连接,用于根据所述上拉控制信号开启或者关闭,并在开启时拉升所述输出信号的电压;

10.升压模块,与所述上拉控制模块连接并与所述第二上拉驱动模块并联,用于根据所述上拉控制信号开启或者关闭,并在开启时拉升所述输出信号的电压;所述第二上拉驱动模块与所述升压模块的合并结构与所述第一上拉驱动器相同并受所述上拉控制信号控制。

11.在其中一个实施例中,所述上拉控制信号为第一上拉控制信号或者第二上拉控制信号,所述第一上拉控制信号用于驱动所述升压模块开启,所述第二上拉控制信号用于驱动所述升压模块和所述第二上拉驱动模块开启;

12.所述上拉控制模块还用于接收标识信号,若所述标识信号处于第一电平,则生成所述第一上拉控制信号;若所述标识信号处于第二电平,则生成所述第二上拉控制信号。

13.在其中一个实施例中,所述第一上拉控制信号和所述第二上拉控制信号均为脉冲信号,所述第一上拉控制信号的脉冲宽度小于所述第二上拉控制信号的脉冲宽度。

14.在其中一个实施例中,所述上拉指示信号为脉冲信号,所述第二上拉控制信号的脉冲宽度与所述上拉指示信号的脉冲宽度相同。

15.在其中一个实施例中,所述上拉控制模块包括:

16.第一逻辑电路,用于接收所述上拉指示信号和所述标识信号,若所述标识信号处

于第一电平,则对所述上拉指示信号进行延迟并取反后输出;若所述标识信号处于第二电平,则输出高电平信号;

17.第二逻辑电路,与所述第一逻辑电路的输出端连接,用于将所述第一逻辑电路的输出信号与所述上拉指示信号进行逻辑与,得到所述上拉控制信号。

18.在其中一个实施例中,所述第一逻辑电路包括:

19.延迟单元,用于接收所述上拉指示信号,并对所述上拉指示信号进行延迟;

20.第一与非门,所述第一与非门的第一输入端与所述延迟单元的输出端连接,所述第一与非门的第二输入端用于接收所述标识信号。

21.在其中一个实施例中,所述第一上拉驱动模块包括:

22.前置驱动器,用于根据上拉指示信号和驱动选择信号,生成多个上拉驱动器控制信号;

23.多个所述第一上拉驱动器,与所述多个上拉驱动器控制信号一一对应,用于接收对应的所述上拉驱动器控制信号,并根据接收到的所述上拉驱动器控制信号进行开启或者关闭。

24.在其中一个实施例中,所述第二上拉驱动模块和所述升压模块通过nmos管拉升所述输出信号的电压。

25.在其中一个实施例中,所述第二上拉驱动模块处于所述第一上拉驱动模块和所述驱动电路的输出端之间。

26.第二方面,还提供了一种传输系统,所述传输系统包括如第一方面提供的驱动电路。

27.上述驱动电路及传输系统,包括第一上拉驱动模块、第二上拉驱动模块、上拉控制模块和升压模块。第一上拉驱动模块包含多个第一上拉驱动器,根据上拉指示信号和驱动选择信号开启至少一个第一上拉驱动器,驱动选择信号用于选择第一上拉驱动器的开启数量,可以根据需要开启部分或者全部的第一上拉驱动器,第一上拉驱动器用于生成具有预设电压的输出信号。而且上拉控制模块根据上拉指示信号生成上拉控制信号,升压模块与上拉控制模块连接,根据上拉控制信号开启或者关闭,在开启时拉升输出信号的电压,并未改变当前驱动电路的结构,可以实现当前驱动电路的功能。另外,第二上拉驱动模块与上拉控制模块连接并与升压模块并联,根据上拉控制信号开启或者关闭,在开启时拉升输出信号的电压,第二上拉驱动模块与升压模块的合并结构与第一上拉驱动器相同并受上拉控制信号控制,可以在第一上拉驱动器全部开启时增加驱动晶体管的并联数量,减小发送器的输出阻抗,并且第二上拉驱动模块与升压模块共用同一信号,不需要相应增加预驱动电路和对应的信号线,引脚连接区域的面积基本没有变化,不会影响到芯片性能。

附图说明

28.为了更清楚地说明本技术实施例或传统技术中的技术方案,下面将对实施例或传统技术描述中所需要使用的附图作简单地介绍,显而易见地,下面描述中的附图仅仅是本技术的一些实施例,对于本领域普通技术人员来讲,在不付出创造性劳动的前提下,还可以根据这些附图获得其他的附图。

29.图1为相关技术中驱动电路的结构示意图;

30.图2为图1中各个脉冲生成器的结构示意图;

31.图3为图2中各个信号的时序图;

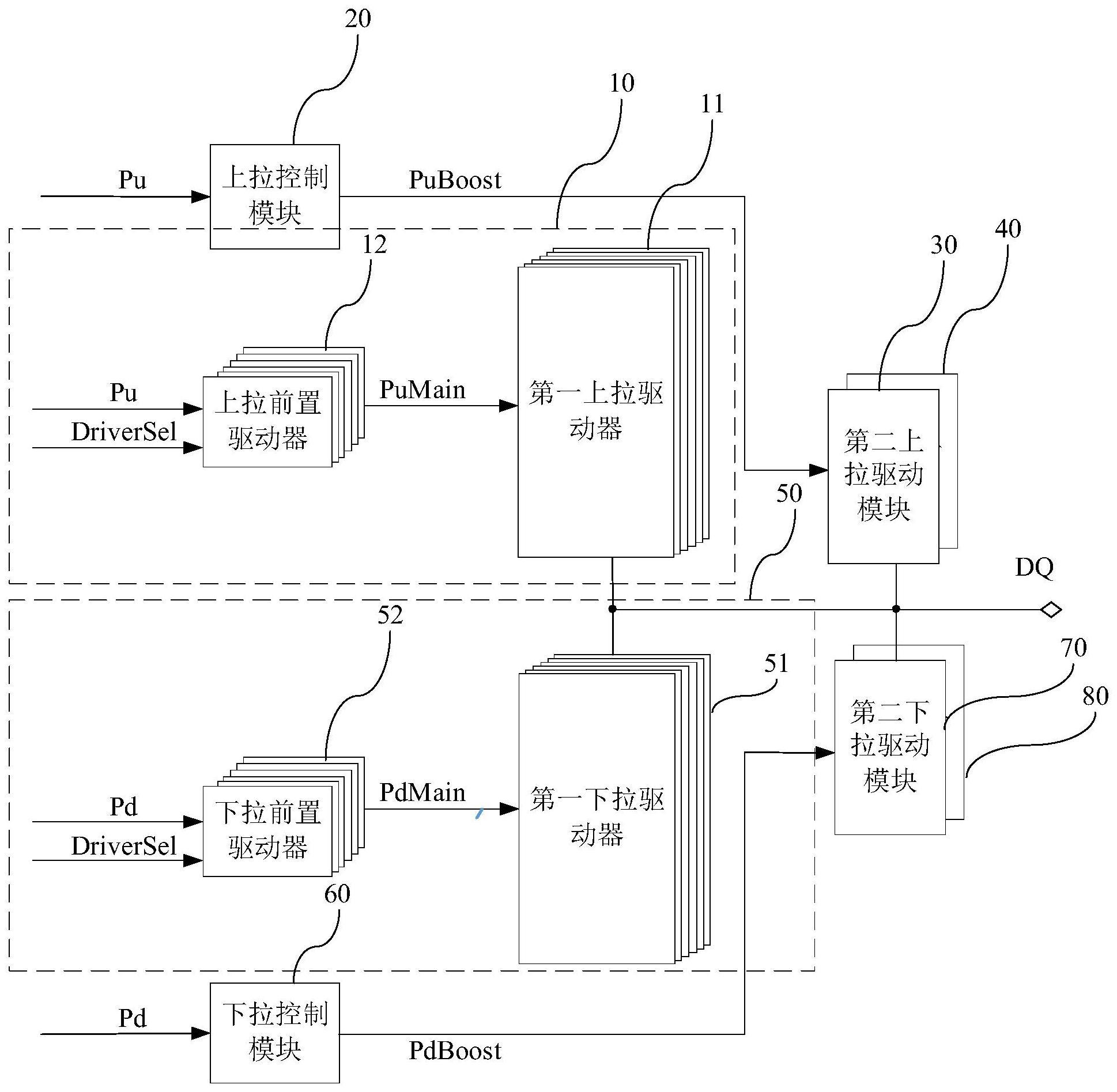

32.图4为一实施例的驱动电路的结构示意图;

33.图5为一实施例的驱动电路中各个信号的时序图;

34.图6为一实施例中上拉控制模块的结构示意图。

35.附图标记说明:

36.101、第一预驱动器,102、上拉驱动器,103、上拉单元,104、第一脉冲生成器,105、第二预驱动器,106、下拉驱动器,107、下拉单元,108、第二脉冲生成器;201、第一级与非门,202、第一级非门,203、第二级非门,204、第二级与非门,205、第三级非门,206、第四级非门;10、第一上拉驱动模块,11、第一上拉驱动器,12、上拉前置驱动器;20、上拉控制模块,21、第一逻辑电路,210、延迟单元,211、第一与非门,212、第二与非门,213、第一非门;22、第二逻辑电路,221、第三与非门,222、第二非门;30、第二上拉驱动模块,40、升压模块;50、第一下拉驱动模块,51、第一下拉驱动器,52、下拉前置驱动器;60、下拉控制模块,70、第二下拉驱动模块,80、降压模块。

具体实施方式

37.为了便于理解本技术,下面将参照相关附图对本技术进行更全面的描述。附图中给出了本技术的实施例。但是,本技术可以以许多不同的形式来实现,并不限于本文所描述的实施例。相反地,提供这些实施例的目的是使本技术的公开内容更加透彻全面。

38.除非另有定义,本文所使用的所有的技术和科学术语与属于本技术的技术领域的技术人员通常理解的含义相同。本文中在本技术的说明书中所使用的术语只是为了描述具体的实施例的目的,不是旨在于限制本技术。

39.可以理解,本技术所使用的术语“第一”、“第二”等可在本文中用于描述各种元件,但这些元件不受这些术语限制。这些术语仅用于将第一个元件与另一个元件区分。举例来说,在不脱离本技术的范围的情况下,可以将第一电阻称为第二电阻,且类似地,可将第二电阻称为第一电阻。第一电阻和第二电阻两者都是电阻,但其不是同一电阻。

40.可以理解,以下实施例中的“连接”,如果被连接的电路、模块、单元等相互之间具有电信号或数据的传递,则应理解为“电连接”、“通信连接”等。

41.在此使用时,单数形式的“一”、“一个”和“所述/该”也可以包括复数形式,除非上下文清楚指出另外的方式。还应当理解的是,术语“包括/包含”或“具有”等指定所陈述的特征、整体、步骤、操作、组件、部分或它们的组合的存在,但是不排除存在或添加一个或更多个其他特征、整体、步骤、操作、组件、部分或它们的组合的可能性。同时,在本说明书中使用的术语“和/或”包括相关所列项目的任何及所有组合。

42.dram芯片包括高速信号发送器。为了增强输出信号的边沿速率(英文:slew rate),一般会在发送器靠近数据端口的位置设置上拉电路和下拉电路。上拉电路和下拉电路均连接在数据线上,组成驱动电路。

43.图1为相关技术中驱动电路的结构示意图,如图1所示,驱动电路中的上拉部分包括多个第一预驱动器101、多个上拉驱动器102、上拉单元103和第一脉冲生成器104。多个第一预驱动器101用于接收上拉指示信号pu和驱动选择信号driversel,并生成上拉驱动器控

制信号pumain。上拉驱动器控制信号pumain包括与多个第一预驱动器101一一对应的子信号,每个第一预驱动器101输出对应的子信号。以6个子信号为例,第2个至第3个子信号相同,第4个至第6个子信号相同。

44.多个上拉驱动器102与数据线dq连接,并与多个第一预驱动器101一一对应连接。多个上拉驱动器102用于接收上拉驱动器控制信号pumain,并根据各自对应的子信号开启或者关闭,并在开启时拉升数据线的输出电压,以输出数据信号。其中,上拉驱动器102的开启数量,会影响到驱动电路的输出阻抗。上拉驱动器102的开启数量越多,驱动电路的输出阻抗越小。

45.第一脉冲生成器104用于接收上拉指示信号pu,并生成上拉控制信号puboost。上拉单元103与第一脉冲生成器104连接,用于接收上拉控制信号puboost,并根据上拉控制信号puboost开启或者关闭,以在开启时拉升数据线的输出电压,从而增强输出信号的上拉边沿速率。

46.类似地,驱动电路中的下拉部分包括多个第二预驱动器105、多个下拉驱动器106、下拉单元107和第二脉冲生成器108。多个第二预驱动器105用于接收下拉指示信号pd和驱动选择信号driversel,并生成下拉驱动器控制信号pdmain。下拉驱动器控制信号pdmain包括与多个第二预驱动器105一一对应的子信号,每个第二预驱动器105输出对应的子信号。以6个子信号为例,第1个至第3个子信号相同,第4个至第5个子信号相同。

47.多个下拉驱动器106与数据线dq连接,并与多个第二预驱动器105一一对应连接。多个下拉驱动器106用于接收下拉驱动器控制信号pdmain,并根据各自对应的子信号开启或者关闭,以在开启时拉低数据线的输出电压。其中,下拉驱动器106的开启数量,会影响到驱动电路的输出阻抗。下拉驱动器106的开启数量越多,驱动电路的输出阻抗越小。

48.第二脉冲生成器108用于接收下拉指示信号pd,并生成下拉控制信号pdboost。下拉单元107与第二脉冲生成器108连接,用于接收下拉控制信号pdboost,并根据下拉控制信号pdboost开启或者关闭,以在开启时拉低数据线的输出电压,从而增强输出信号的下拉边沿速率。

49.图2为图1中各个脉冲生成器的结构示意图,如图2所示,第一脉冲生成器104和第二脉冲生成器108均包括依次级联的第一级与非门201、第一级非门202、第二级非门203、第二级与非门204、第三级非门205和第四级非门206。第一级与非门201的两个输入端分别用于接收输入信号din和使能信号en,输入信号为din上拉指示信号pu或者下拉指示信号pd。第一级非门202的输入端用于接收第一级与非门201的输出信号。第二级非门203的输入端用于接收第一级非门202的输出信号。第二级与非门204的两个输入端分别用于接收输入信号din和第二级非门203的输出信号int。第三级非门205的输入端用于接收第二级与非门204的输出信号。当输入信号din为上拉指示信号pu时,第三级非门205的输出信号dout为上拉控制信号puboost;当输入信号din为下拉指示信号pd时,第三级非门205的输出信号dout为下拉控制信号pdboost。

50.图3为图2中各个信号的时序图,如图3所示,输入信号din、第二级非门203的输出信号int、第三级非门205的输出信号dout均为脉冲信号,第二级非门203的输出信号int为输入信号din延迟后取反,第三级非门205的输出信号dout为输入信号din和第二级非门203的输出信号int逻辑与。

51.联合电子设备工程委员会(英文:joint electron device engineering council,简称:jedec)之前规定驱动电路的输出阻抗最低为40ω,此时上拉驱动器102或者下拉驱动器106的开启数量为6个。随着dram速度的提高,为了使信号能够达到足够的摆幅,需要进一步减小发送器的输出阻抗,如由40ω减小到34ω,此时上拉驱动器102或者下拉驱动器106的开启数量需要增加到7个。但是增加上拉驱动器102和下拉驱动器106的数量,需要相应增加第一预驱动器101、第二预驱动器105、以及对应的信号线,使得引脚连接区域的面积增大较多,影响芯片性能。

52.基于上述情况,本发明提供了一种驱动电路及传输系统,在相关技术的基础上进行改进,可以达到增加驱动晶体管的并联数量的效果,减小发送器的输出阻抗,并且不需要相应增加预驱动电路和开关电路、以及对应的信号线等,引脚连接区域的面积基本没有变化,不会影响到芯片性能。

53.图4为一实施例的驱动电路的结构示意图,如图4所示,驱动电路包括第一上拉驱动模块10、上拉控制模块20、第二上拉驱动模块30和升压模块40。第一上拉驱动模块10包含多个第一上拉驱动器11,用于根据上拉指示信号pu和驱动选择信号driversel开启至少一个第一上拉驱动器11。驱动选择信号driversel用于选择第一上拉驱动器11的开启数量。第一上拉驱动器11用于生成具有预设电压的输出信号。上拉控制模块20用于根据上拉指示信号pu生成上拉控制信号puboost。第二上拉驱动模块30与上拉控制模块20连接,用于根据上拉控制信号puboost开启或者关闭,并在开启时拉升输出信号的电压。升压模块40与上拉控制模块20连接并与第二上拉驱动模块30并联,用于根据上拉控制信号puboost开启或者关闭,并在开启时拉升输出信号的电压。第二上拉驱动模块30与升压模块40的合并结构与第一上拉驱动器11相同并受上拉控制信号puboost控制。

54.上述实施例中,驱动电路包括第一上拉驱动模块10、第二上拉驱动模块30、上拉控制模块20和升压模块40。第一上拉驱动模块10包含多个第一上拉驱动器11,根据上拉指示信号pu和驱动选择信号driversel开启至少一个第一上拉驱动器11,驱动选择信号driversel用于选择第一上拉驱动器11的开启数量,可以根据需要开启部分或者全部的第一上拉驱动器11,第一上拉驱动器11用于生成具有预设电压的输出信号。而且上拉控制模块20根据上拉指示信号pu生成上拉控制信号puboost,升压模块40与上拉控制模块20连接,根据上拉控制信号puboost开启或者关闭,在开启时拉升输出信号的电压,并未改变当前驱动电路的结构,可以实现当前驱动电路的功能。另外,第二上拉驱动模块30与上拉控制模块20连接并与升压模块40并联,根据上拉控制信号puboost开启或者关闭,在开启时拉升输出信号的电压,第二上拉驱动模块30与升压模块40的合并结构与第一上拉驱动器11相同并受上拉控制信号puboost控制,可以在第一上拉驱动器11全部开启时增加驱动晶体管的并联数量,减小发送器的输出阻抗,并且控制信号与升压模块共用同一信号,不需要相应增加预驱动电路和对应的信号线,引脚连接区域的面积基本没有变化,不会影响到芯片性能。

55.由此可见,本发明是在原来升压模块的位置设置第一上拉驱动器,并且可以对第一上拉驱动器进行部分使能和全部使能,部分使能时的使能部分相当于原来的升压模块,全部使能时的使能部分起到第一上拉驱动器的作用,以降低阻抗。而且这个位置距离输出端比较近,能够起到提升边沿速率的作用。

56.其中,上拉指示信号pu为使能信号,可以控制第一上拉驱动器11的开闭状态。若上

拉指示信号pu处于有效电平,则控制至少一个第一上拉驱动器11开启;若上拉指示信号pu处于无效电平,则控制所有的第一上拉驱动器11关闭。

57.在实际应用中,第一上拉驱动模块10中的至少两个第一上拉驱动器11的开闭状态保持一致。对于开闭状态一致的至少两个上拉驱动器11而言,当其中任意一个第一上拉驱动器11处于开启状态,其它的第一上拉驱动器11也处于开启状态。当其中任意一个上拉驱动器处于关闭状态,其它的第一上拉驱动器11也处于关闭状态。在此基础上,由驱动选择信号driversel选择第一上拉驱动器11的开启数量,即可确定开启哪些第一上拉驱动器11。例如,第一上拉驱动模块10包含6个第一上拉驱动器11,第1个至第3个第一上拉驱动器11的开闭状态保持一致,第4个至第5个第一上拉驱动器11的开闭状态保持一致。如果第一上拉驱动器11的开启数量为1,则开启第6个第一上拉驱动器11;如果第一上拉驱动器11的开启数量为2,则开启第4个至第5个第一上拉驱动器11;如果第一上拉驱动器11的开启数量为3,则开启第1个至第3个第一上拉驱动器11;如果第一上拉驱动器11的开启数量为4,则开启第1个至第3个第一上拉驱动器11、以及第6个第一上拉驱动器11;如果第一上拉驱动器11的开启数量为5,则开启第1个至第5个第一上拉驱动器11;如果第一上拉驱动器11的开启数量为6,则开启第1个至第6个第一上拉驱动器11。

58.示例性地,第一上拉驱动器11、第二上拉驱动模块30和升压模块40均包括驱动晶体管。第一上拉驱动模块10还包括逻辑控制电路,如解码器。

59.可选地,驱动晶体管可以为n型金属氧化物半导体(negative channel metal oxide semiconductor,简称nmos)管,也可以为p型金属氧化物半导体(positive channel metal oxide semiconductor,简称pmos)。

60.在一个实施例中,第二上拉驱动模块30处于第一上拉驱动模块10和驱动电路的输出端dq之间,第一上拉驱动模块10可以保持不变,不需要相应增加预驱动电路和对应的信号线,引脚连接区域的面积基本没有变化,不会影响到芯片性能。可选地,第二上拉驱动模块30和升压模块40通过nmos管拉升输出信号的电压,可以减小寄生电容。

61.在一个实施例中,上拉控制信号puboost为第一上拉控制信号puboost1或者第二上拉控制信号puboost2,第一上拉控制信号puboost1用于驱动升压模块40开启,第二上拉控制信号puboost2用于驱动升压模块40和第二上拉驱动模块30开启。上拉控制模块20还用于接收标识信号rowswitchn;若标识信号rowswitchn处于第一电平,则生成第一上拉控制信号puboost1;若标识信号rowswitchn处于第二电平,则生成第二上拉控制信号puboost2。

62.上述实施例中,通过将上拉控制信号puboost划分为第一上拉控制信号puboost1和第二上拉控制信号puboost2两种,第一上拉控制信号puboost1驱动升压模块40开启,此时可以实现当前驱动电路的功能;第二上拉控制信号puboost2驱动升压模块40和第二上拉驱动模块30开启,此时的等效电路与升压模块40开启时多开启一个第一上拉驱动器11相同。这样利用第二上拉驱动模块30和升压模块40的配合,可以在当前驱动电路的基础上实现增加一个驱动晶体管并联的效果。

63.而上拉控制模块20还接收标识信号rowswitchn,并根据标识信号rowswitchn的电平,生成第一上拉控制信号puboost1或者第二上拉控制信号puboost2作为上拉控制信号puboost,这样通过标识信号rowswitchn选择生成不同的上拉控制信号puboost,从而进入不同的模式,生成第一上拉控制信号puboost1实现当前驱动电路的功能,生成第二上拉控

制信号puboost2在当前驱动电路的基础上实现增加并联驱动晶体管数量、降低阻抗的效果。

64.图5为一实施例的驱动电路中各个信号的时序图,如图5所示,在一个实施例中,第一上拉控制信号puboost1和第二上拉控制信号puboost2均为脉冲信号,第一上拉控制信号puboost1的脉冲宽度小于第二上拉控制信号puboost2的脉冲宽度。

65.在实际应用中,驱动晶体管导通的脉冲信号宽度可以不同。上述实施例中,通过将第一上拉控制信号puboost1和第二上拉控制信号puboost2设置为脉冲宽度不同的脉冲信号,可以利用脉冲宽度较小的第一上拉控制信号puboost1仅控制升压模块40中的驱动晶体管导通,脉冲宽度较大的第二上拉控制信号puboost2使得第二上拉驱动模块30和升压模块40中的驱动晶体管均导通。

66.如图5所示,在一个实施例中,上拉指示信号pu为脉冲信号,第二上拉控制信号puboost2的脉冲宽度与上拉指示信号pu的脉冲宽度相同。

67.上述实施例中,第二上拉控制信号puboost2与上拉指示信号pu为脉冲宽度相同的脉冲信号,方便根据上拉指示信号pu生成第二上拉控制信号puboost2。

68.图6为一实施例中上拉控制模块的结构示意图,如图6所示,在一个实施例中,上拉控制模块20包括第一逻辑电路21和第二逻辑电路22。第一逻辑电路21用于,接收上拉指示信号pu和标识信号rowswitchn;若标识信号rowswitchn处于第一电平,则对上拉指示信号pu进行延迟并取反后输出;若标识信号rowswitchn处于第二电平,则输出高电平信号。第二逻辑电路22与第一逻辑电路21的输出端连接,用于将第一逻辑电路21的输出信号与上拉指示信号pu进行逻辑与,得到上拉控制信号puboost。

69.上述实施例中,通过将上拉控制模块20划分为第一逻辑电路21和第二逻辑电路22,第一逻辑电路21根据标识信号rowswitchn由上拉指示信号pu输出不同的中间信号int,第二逻辑电路22由中间信号int和上拉指示信号pu得到上拉控制信号puboost,从而实现上拉控制模块20的功能。

70.如图6所示,可选地,第一逻辑电路21包括延迟单元210和第一与非门211。延迟单元210用于接收上拉指示信号pu,并对上拉指示信号pu进行延迟。第一与非门211的第一输入端与延迟单元210的输出端连接,第一与非门211的第二输入端用于接收标识信号rowswitchn。

71.上述实施例中,第一逻辑电路21包括延迟单元210和第一与非门211,延迟单元210可以对上拉指示信号pu进行延迟,第一与非门211的第一输入端与延迟单元210的输出端连接,第一与非门211的第二输入端用于接收标识信号rowswitchn,即可标识信号rowswitchn处于第一电平时对上拉指示信号pu进行延迟并取反后输出,并在标识信号rowswitchn处于第二电平时输出高电平信号。

72.如图6所示,示例性地,延迟单元210包括第二与非门212和第一非门213,第二与非门212的第一输入端用于接收上拉指示信号pu,第二与非门212的第二输入端用于接收使能信号en,第二与非门212的输出端与第一非门213的输入端连接,第一非门213的输出端与第一与非门211的输入端连接。

73.如图6所示,示例性地,第二逻辑电路22包括第三与非门221和第二非门222,第三与非门221的第一输入端用于接收上拉指示信号pu,第三与非门221的第二输入端与第一与

非门211的输出端连接,第三与非门221的输出端与第二非门222的输入端连接,第二非门222的输出端用于输出上拉控制信号puboost。

74.上述实施例中,通过第三与非门221和第二非门222实现逻辑与,可以配合延迟单元210实现延迟功能。

75.如图4所示,在一个实施例中,第一上拉驱动模块10还包括上拉前置驱动器12。上拉前置驱动器12用于根据上拉指示信号pu和驱动选择信号driversel,生成多个上拉驱动器控制信号pumain。多个第一上拉驱动器11与多个上拉驱动器控制信号pumain一一对应,用于接收对应的上拉驱动器控制信号pumain,并根据接收到的上拉驱动器控制信号pumain进行开启或者关闭。

76.上述实施例中,前置驱动器12用于根据上拉指示信号pu和驱动选择信号driversel,生成与多个第一上拉驱动器11一一对应的多个上拉驱动器控制信号pumain,可以分别控制各个第一上拉驱动器11开启或者关闭。

77.示例性地,前置驱动器12可以包括与多个第一上拉驱动器11一一对应的驱动晶体管。

78.如图4所示,在一个实施例中,驱动电路还包括第一下拉驱动模块50、下拉控制模块60、第二下拉驱动模块70和降压模块80。第一下拉驱动模块50包含多个第一下拉驱动器51,用于根据下拉指示信号pd和驱动选择信号driversel开启至少一个第一下拉驱动器51。驱动选择信号driversel用于选择第一下拉驱动器51的开启数量。第一下拉驱动器51用于生成具有预设电压的输出信号。下拉控制模块60用于根据下拉指示信号pd生成下拉控制信号pdboost。第二下拉驱动模块70与下拉控制模块60连接,用于根据下拉控制信号pdboost开启或者关闭,并在开启时拉低输出信号的电压。降压模块80与下拉控制模块60连接并与第二下拉驱动模块70并联,用于根据下拉控制信号pdboost开启或者关闭,并在开启时拉低输出信号的电压。第二下拉驱动模块70与降压模块80的合并结构与第一下拉驱动器51相同并受下拉控制信号pdboost控制。

79.上述实施例中,驱动电路还包括第一下拉驱动模块50、下拉控制模块60、第二下拉驱动模块70和降压模块80。第一下拉驱动模块50包含多个第一下拉驱动器51,根据下拉指示信号pd和驱动选择信号driversel开启至少一个第一下拉驱动器51,驱动选择信号driversel用于选择第一下拉驱动器51的开启数量,可以根据需要开启部分或者全部的第一下拉驱动器,第一下拉驱动器51用于生成具有预设电压的输出信号。而且下拉控制模块60根据下拉指示信号pd生成下拉控制信号pdboost,降压模块80与下拉控制模块60连接,根据下拉控制信号pdboost开启或者关闭,在开启时拉低输出信号的电压,并未改变当前驱动电路的结构,可以实现当前驱动电路的功能。另外,第二下拉驱动模块70与下拉控制模块60连接并与降压模块80并联,根据下拉控制信号pdboost开启或者关闭,在开启时拉低输出信号的电压,第二下拉驱动模块70与降压模块80的合并结构与第一下拉驱动器51相同并受下拉控制信号pdboost控制,可以在第一下拉驱动器51全部开启时增加驱动晶体管的并联数量,减小发送器的输出阻抗,并且控制信号与降压模块共用同一信号,不需要相应增加预驱动电路和对应的信号线,引脚连接区域的面积基本没有变化,不会影响到芯片性能。

80.由此可见,本发明是在原来降压模块的位置设置第一下拉驱动器,并且可以对第一下拉驱动器进行部分使能和全部使能,部分使能时的使能部分相当于原来的降压模块,

全部使能时的使能部分起到第一下拉驱动器的作用,以降低阻抗。而且这个位置距离输出端比较近,能够起到提升边沿速率的作用。

81.如图4所示,在一个实施例中,第一下拉驱动模块50还包括下拉前置驱动器52。下拉前置驱动器52用于根据下拉指示信号pd和驱动选择信号driversel,生成多个下拉驱动器控制信号pdmain。多个第一下拉驱动器51与多个下拉驱动器控制信号pdmain一一对应,用于接收对应的下拉驱动器控制信号pdmain,并根据接收到的下拉驱动器控制信号pdmain进行开启或者关闭。

82.示例性地,第一下拉驱动模块50的结构可以与上述任一实施例提供的第一上拉驱动模块10相同,下拉控制模块60的结构可以与上述任一实施例提供的上拉控制模块20相同,第二下拉驱动模块70的结构可以与上述任一实施例提供的第二上拉驱动模块30相同,降压模块80可以与上述任一实施例提供的升压模块40相同。

83.基于同样的发明构思,本发明还提供了一种驱动电路,驱动电路包括上述任一实施例提供的第一下拉驱动模块、下拉控制模块、第二下拉驱动模块和降压模块。

84.基于同样的发明构思,本发明还提供了一种传输系统,传输系统包括上述任一实施例提供的驱动电路。

85.在本说明书的描述中,参考术语“有些实施例”、“其他实施例”、“理想实施例”等的描述意指结合该实施例或示例描述的具体特征、结构、材料或者特征包含于本发明的至少一个实施例或示例中。在本说明书中,对上述术语的示意性描述不一定指的是相同的实施例或示例。

86.以上所述实施例的各技术特征可以进行任意的组合,为使描述简洁,未对上述实施例中的各个技术特征所有可能的组合都进行描述,然而,只要这些技术特征的组合不存在矛盾,都应当认为是本说明书记载的范围。

87.以上所述实施例仅表达了本发明的几种实施方式,其描述较为具体和详细,但并不能因此而理解为对发明专利范围的限制。应当指出的是,对于本领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干变形和改进,这些都属于本发明的保护范围。因此,本发明专利的保护范围应以所附权利要求为准。

当前第1页1

相关技术

网友询问留言

已有0条留言

- 还没有人留言评论。精彩留言会获得点赞!